交大修課心得 - 數位電路實驗

課程綱要

課程名稱:(中文授課)數位電路實驗

授課教師:蔡淳仁

修課年度:107上 資工系 – 必修

使用書籍:無

心得

教了什麼

共有 8 次 LAB,大部分都在 FPGA 上操作:

- Matrix multiplication (Simulator)

- De-bouncing circuit & LED control (FPGA)

- 1602 Text LCD control (FPGA)

- UART communications (FPGA)

- Matrix multiplication for real (FPGA)

- SD card data-reading (FPGA)

- Passkey cracking (FPGA)

- VGA video display (FPGA)

上課會講一些硬體相關的知識:

- The Verilog HDL for Synthesizable Designs (教你怎麼寫 Verilog)

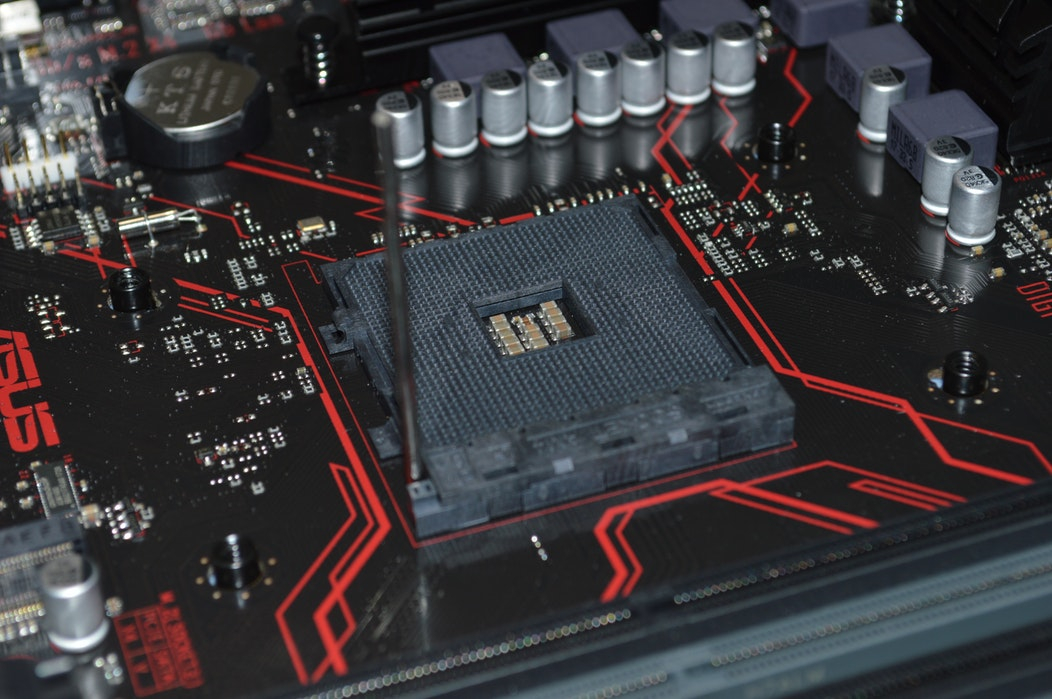

- FPGA (介紹 FPGA、運作原理)

- Register Transfer Level Designs (我沒有聽很懂)

- FPGA Design Techniques (介紹一些 Optimize 的方法)

上課方式

每 1 ~ 2 周會有主題,老師會在課堂上介紹一下這次的 LAB 及注意事項,在週間自己找時間進 LAB 做完,上機的時候 DEMO 給助教看成果,助教會問你一些問題然後評分。

做完 LAB 不用交結報 (太體貼學生了)

考試作業

- 期中上機考 (20%)

- 期末上機考 (20%)

- 8 次 LAB (60%)

期中期末考像是小專題的感覺,就是把之前學到的東西組合再一起,題目引導你慢慢把 Code 從簡單到複雜,不會跟你說要做什麼之後就不管你了。

後記

DLAB 大概是目前修過最累的課了,主要原因是因為每次寫完 code 要 gen bit file 傳到 FPGA 上執行時都要等很久,到後面整個規模越來越大時,run 一次等個 5 分鐘都是常有的事,自己做 LAB 的時間有大概超過 5 成的時間都在等他 generate bit file。

後來我選擇的策略是先規劃整個 FSM 的架構,然後在宿舍把能寫的部分就先寫完,而且跑完模擬確認沒什麼大問題之後,才到實驗室把一些需要 FPGA 才能完成的 code 補上,最後才 gen bit file。

就算如此,debug 的過程還是真的很痛苦,在 FPGA 上要 run 對,不只 code 要正確,有些時候甚至是硬體有問題,自己也無從檢查,只能換另外一台跑跑看。

總而言之,DLAB 是一門要花很多時間的一門科目,我自己甚至有一次 LAB 直接做到隔天早上才做完剛好吃早餐…,認真修過這門課後,會對 HDL 有基本的認識,並且可以培養自己的耐心以及對 Project 整體的規劃能力:)聽說之後計組也會需要用到 verilog,如果有先修過這門課應該會有更好的基礎吧。