1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

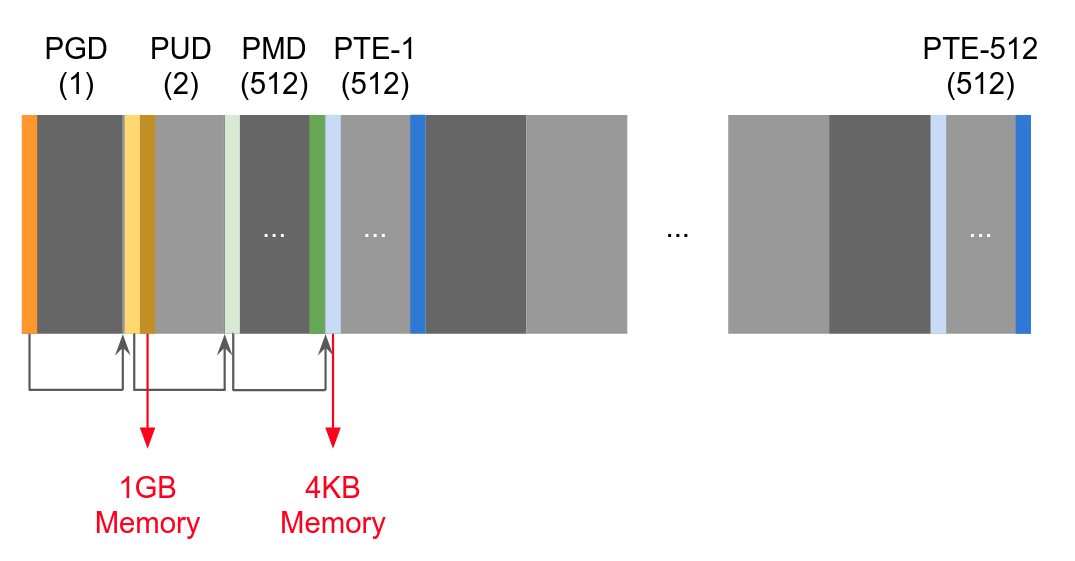

| page_table_create:

/*

* Each page table base address:

* x0: PGD (1 page, 1 entry)

* x1: PUD (1 page, 2 entry)

* x2: PMD (1 page, 512 entry)

* x3: PTE (512 page, each with 512 entry)

*/

ldr x0, =pg_dir

lsl x0, x0, #16 // omit first 16 bit (using physical address)

lsr x0, x0, #16

add x1, x0, #PAGE_SIZE

add x2, x1, #PAGE_SIZE

add x3, x2, #PAGE_SIZE

// setup PGD

ldr x4, =PGD0_ATTR

orr x4, x1, x4 // PUD physical address

str x4, [x0]

// setup PUD1

ldr x4, =PUD0_ATTR

orr x4, x2, x4 // PMD physical address

str x4, [x1]

// setup PUD2 (1GB section start from 0x40000000)

ldr x4, =PUD1_ATTR

mov x5, 0x40000000

orr x4, x5, x4

str x4, [x1, #8]

// setup PMD (512 entry in 1 page)

mov x4, x3 // point to current PTE address

mov x5, xzr // i = 0

mov x6, #512

1:

ldr x7, =PMD0_ATTR

orr x7, x4, x7 // PTE physical address

str x7, [x2, x5, lsl #3] // (i * 8)

add x5, x5, #1

add x4, x4, #PAGE_SIZE

cmp x5, x6

b.ls 1b

// setup normal PTE (512 * 512 - 4096 = 258048 entry)

mov x4, xzr // physical address

mov x5, xzr // i = 0

mov x6, #258048

2:

ldr x7, =PTE_RAM_ATTR

orr x7, x4, x7

str x7, [x3, x5, lsl #3] // (i * 8)

add x5, x5, #1

add x4, x4, #PAGE_SIZE

cmp x5, x6

b.ls 2b

// setup device PTE (16MB = 4096 entry)

add x6, x6, #4096 // 262144

3:

ldr x7, =PTE_MMIO_ATTR

orr x7, x4, x7

str x7, [x3, x5, lsl #3] // (i * 8)

add x5, x5, #1

add x4, x4, #PAGE_SIZE

cmp x5, x6

b.ls 3b

msr ttbr0_el1, x0 // load PGD to the buttom translation based register.

msr ttbr1_el1, x0 // load PGD to the upper translation based register.

ret

|