Exception Level Switch

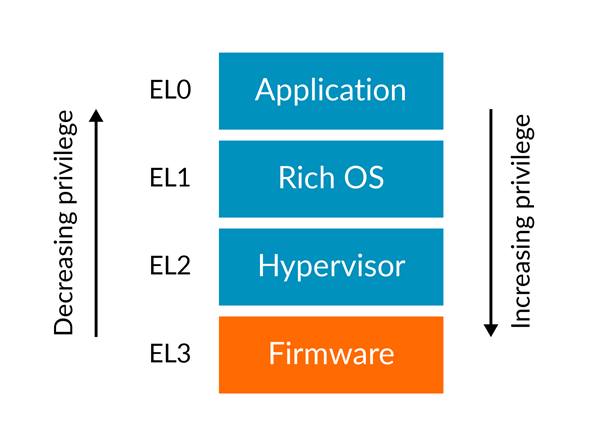

Pi 剛開機後預設會跑在 EL2 上,我們希望將 kernel 跑在 EL1,shell 跑在 EL0,用以區隔 user privilege 與 kernel privilege。

ARM 的硬體設計:

初始化

首先需要對 System Registers 做一些基礎設定:

- SCTLR_EL1 (System Control Register (EL1))

- 把 MMU 關掉

- CPACR_EL1 (Architectural Feature Access Control Register)

- 設定 FPEN (參考雷)

- HCR_EL2

- 設定為 AArch64

- VBAR_EL1 (Vector Base Address Register (EL1))

- 設定 EL1 的 Vector Table

我將一些需要初始化的系統暫存器的值放在 include/sysreg.h 方便之後做調整。

| |

start.S

從 EL2 回到 EL1 的技巧是先設定 spsr_el2 與 elr_el2 並執行 eret。從 EL1 回到 EL0 也是相同技巧。

目前先將 EL1 的 stack 設在 0x60000,EL0 的 stack 設在 0x40000。並設定 EL1 的 Exception Vector Table。

| |

EL1 訪問 Floating Point 及 Advanced SIMD

發現當執行 floating point 相關的指令時 (e.g. ucvtf) 就會進到 Synchronous Exception,查了一下資料才發現要清 CPACR_EL1.FPEN

https://developer.arm.com/docs/ddi0595/b/aarch64-system-registers/cpacr_el1#FPEN